13. A Closed Loop In-Plane Movable Suspended

Gate FET (CLIP-SGFET) Sensor with a Dynamically Reconfigurable Charge pump

(with Pramod Martha, Ganga K. M., Anju Sebastian and Seena V )

IEEE Sensors Journal, vol. 22 issue 15, Nov. 2022

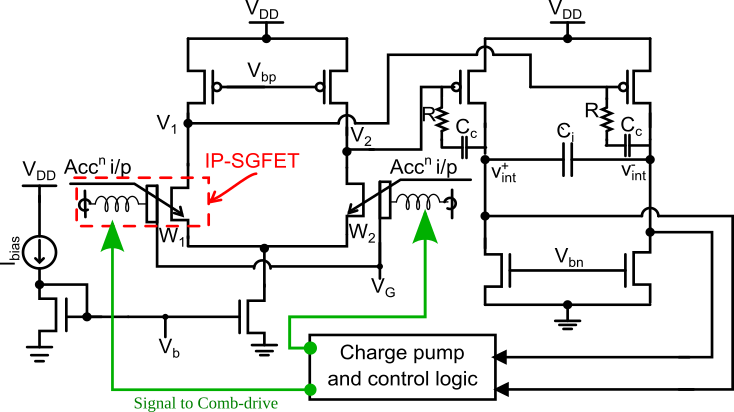

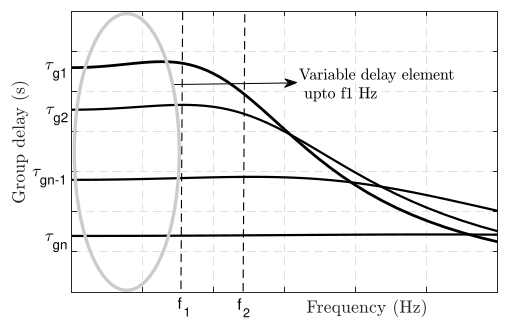

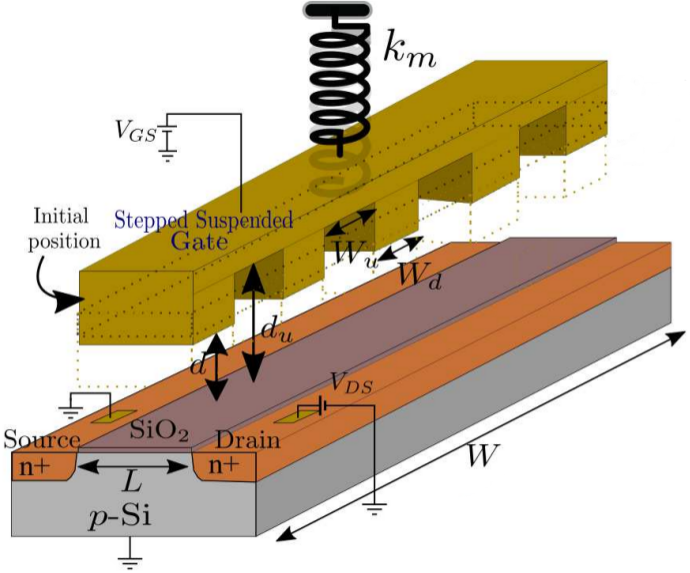

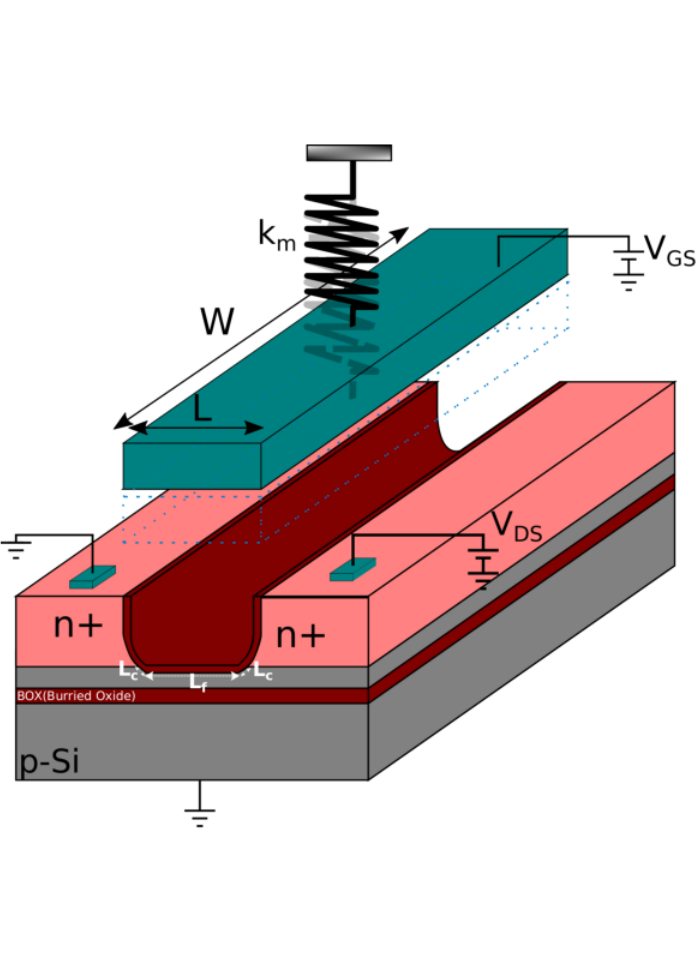

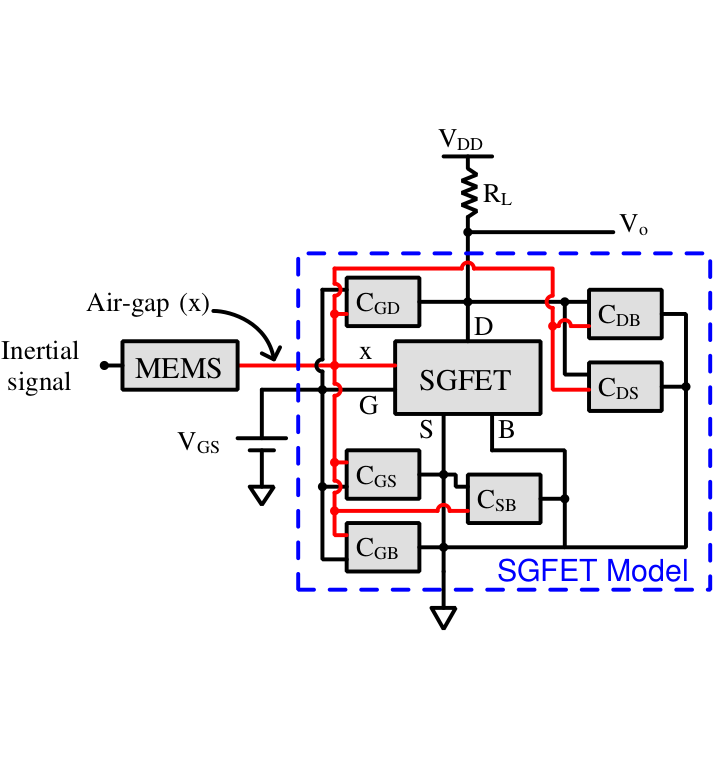

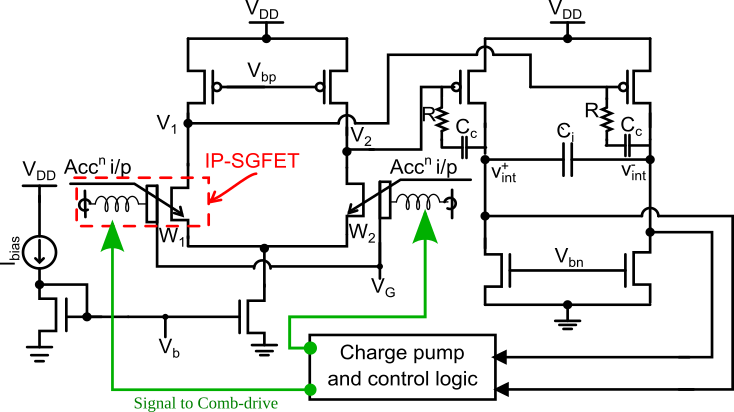

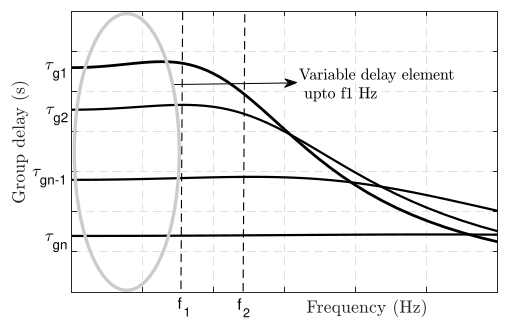

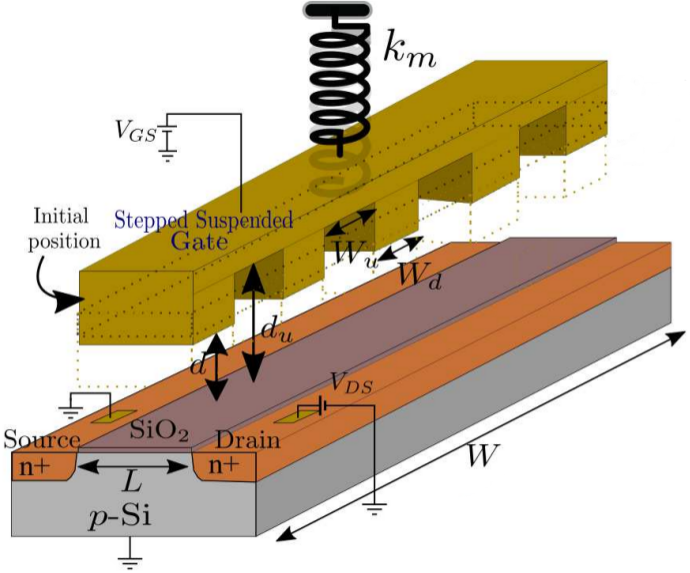

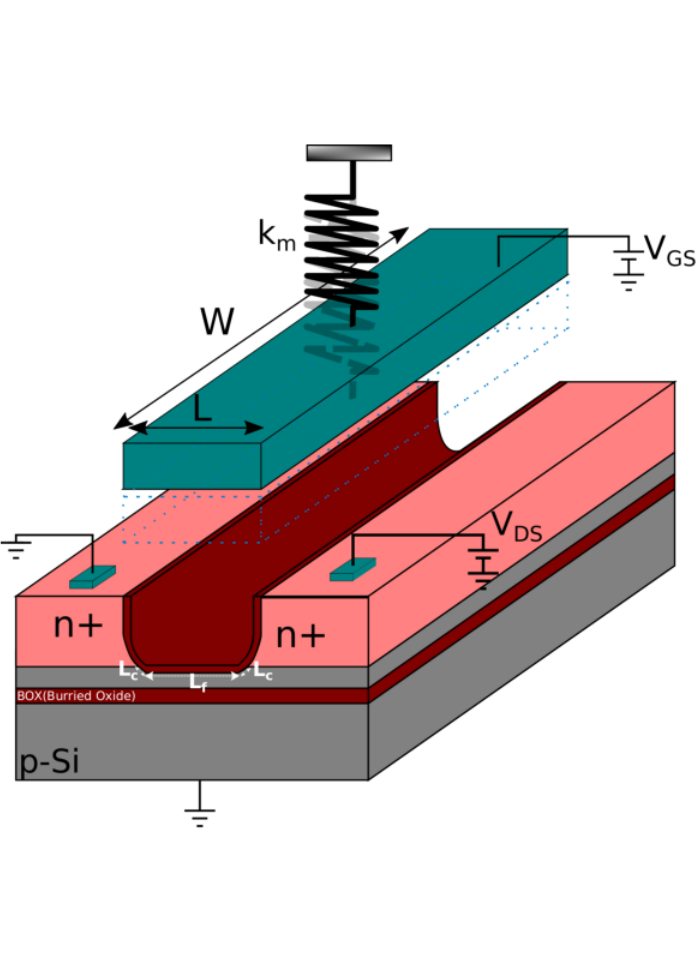

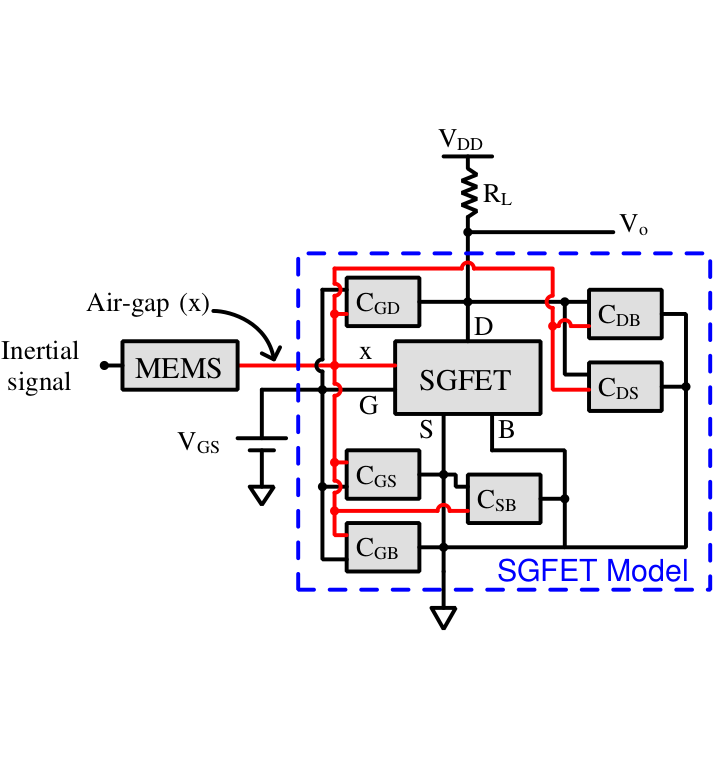

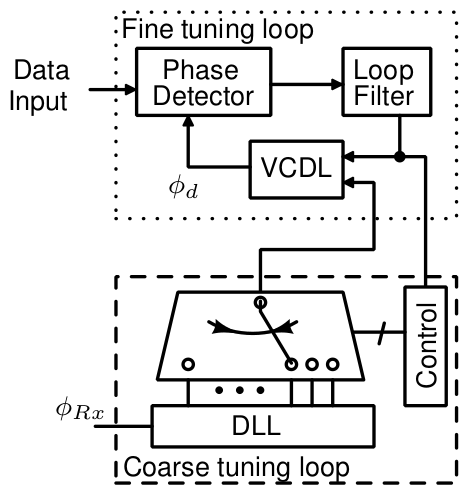

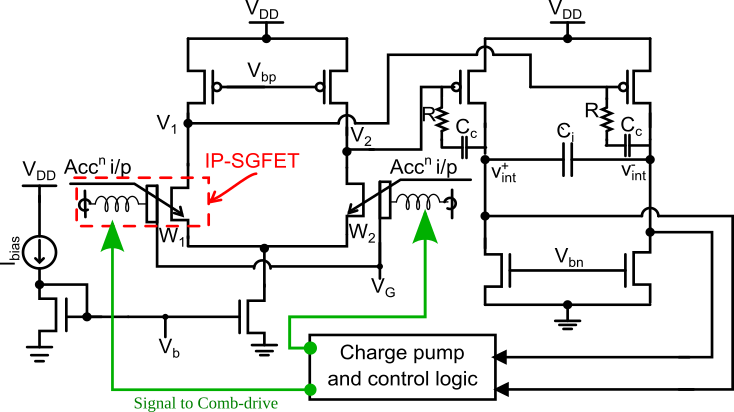

In this paper, we discuss the device, circuit and system design of a closed loop accelerometer

sensor using an in-plane movable suspended gate FET. The paper is comprehensive and discusses

device architecture, simulation methods adopted (we use the Look-up-table method we reported in

paper 9 below), circuit design for the sensor, and a suggested fabrication plan for the sensor.

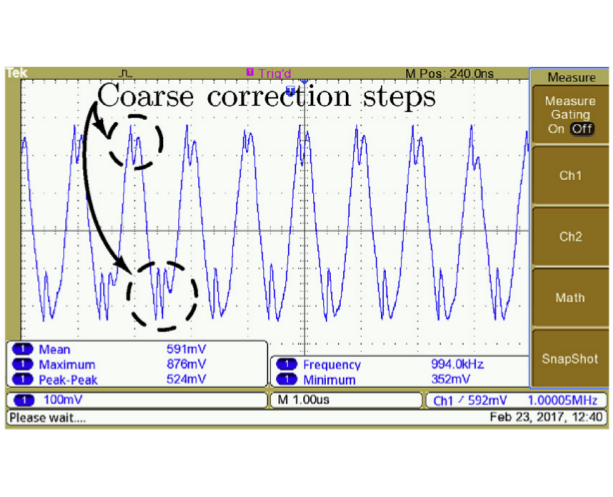

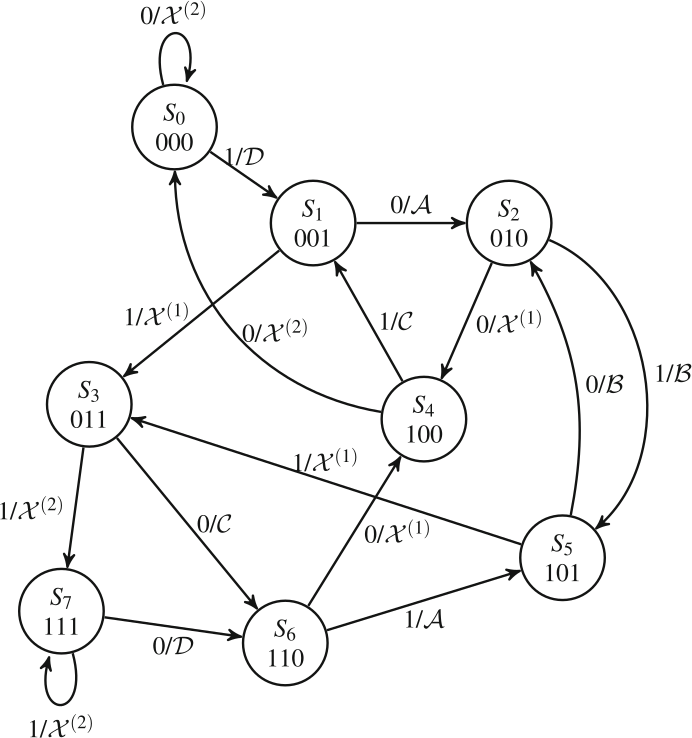

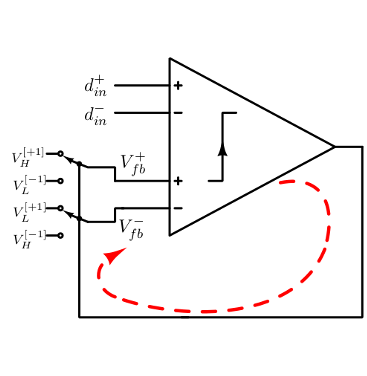

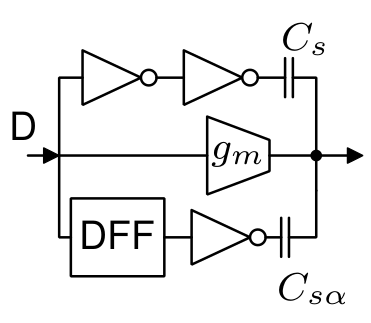

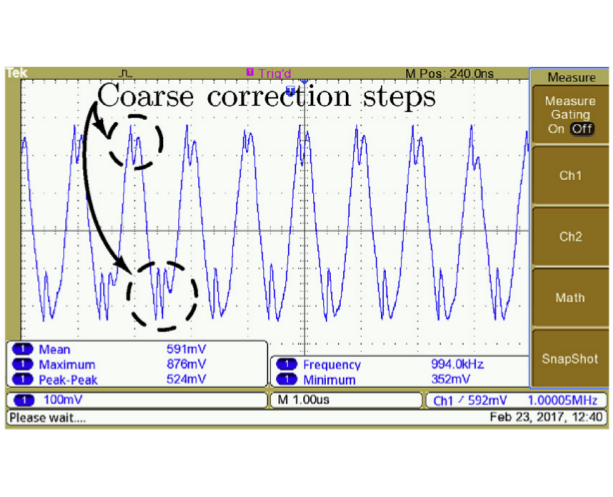

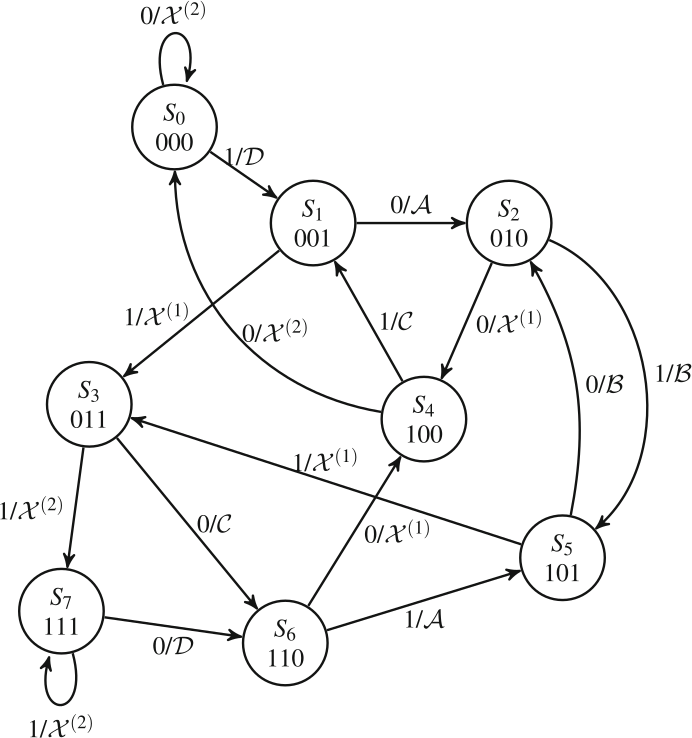

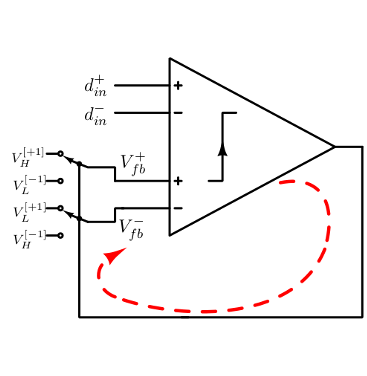

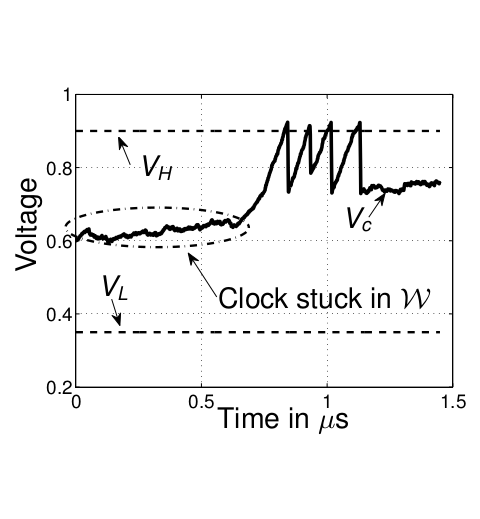

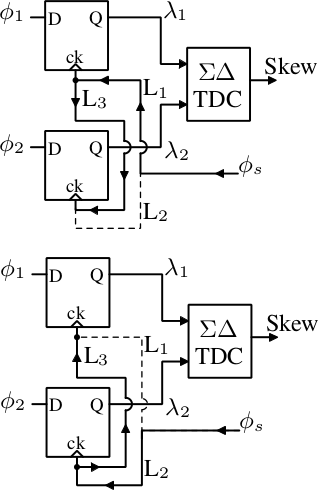

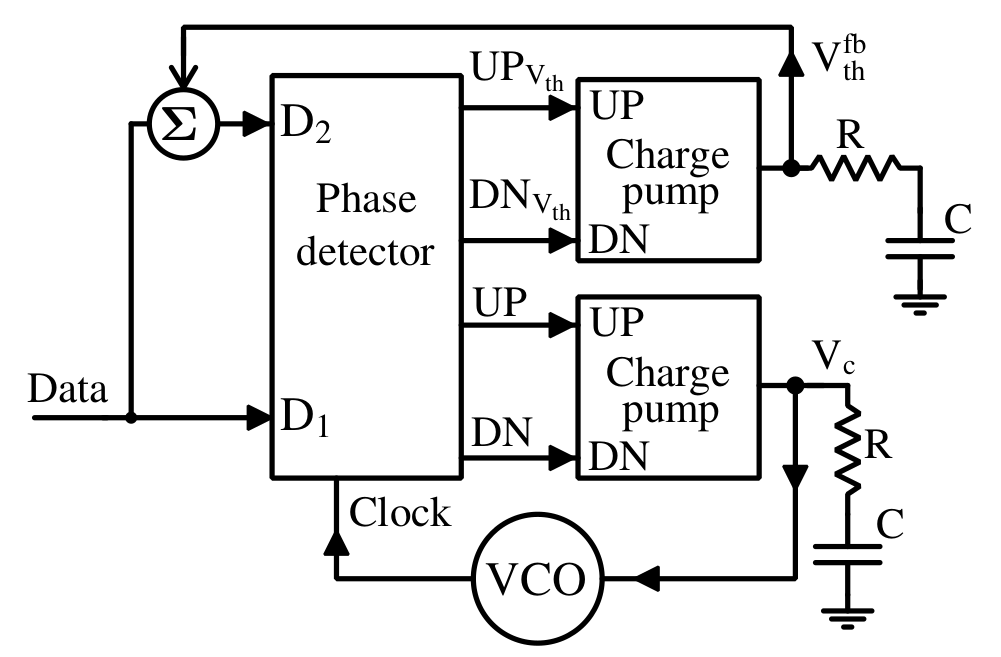

Interface circuits involve novel re-configurable charge pumps for driving actuators in closed loop

operation. We use fully differential architecture which requires two charge pumps for generating

differential actuator drive along with a high voltage common mode feedback circuit. All circuits are

designed in a standard low voltage CMOS process.

--

DOI: https://doi.org/10.1109/TED.2021.3101997

|

|